Prabhjot Bhathal

- Engineer

- San Jose State University

Available

Remote

Student pursuing masters in Electrical Engineering and specializing in ASIC/VLSI/Digital Design and Verification. Graduating in May 2018.

- San Jose, CA

- 0 Years Experience

- prabhjotbhathal

Projects

TRANSMISSION GATE LOGIC BASED 32:1 MU...

by Prabhjot Bhathal

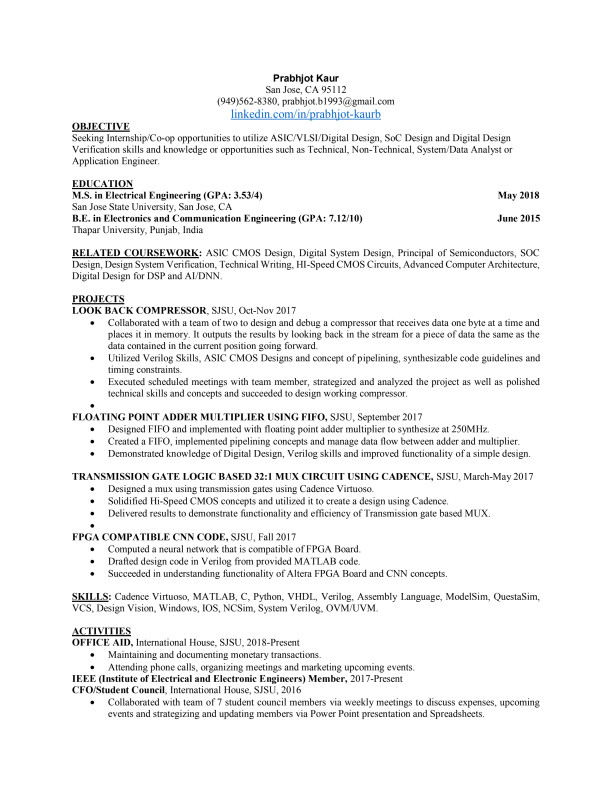

64-Bit CONDITIONAL SUM and CARRY SELE...

by Prabhjot Bhathal

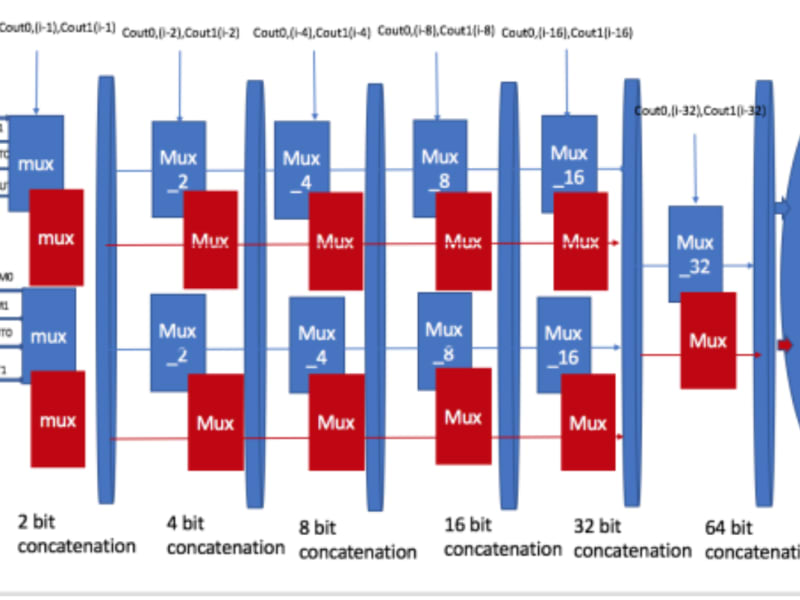

FLOATING POINT ADDER MULTIPLIER USING...

by Prabhjot Bhathal

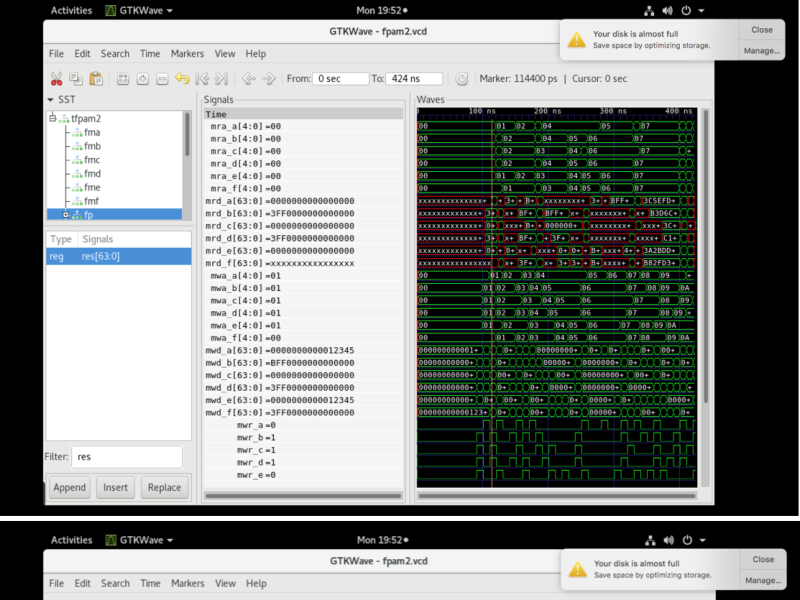

LOOK BACK COMPRESSOR, SJSU, Oct-Nov 2...

by Prabhjot Bhathal